Headsail SoC Tapeout

24th September 2024

As part of the SoC Hub project, the CPC research group successfully taped out a customized TTA-based Digital Signal Processor (DSP). The processor, which we named Beaivi, was fully designed and C-programmed by the group using the TCE/OpenASIP tools developed by the group since the early 2000s.

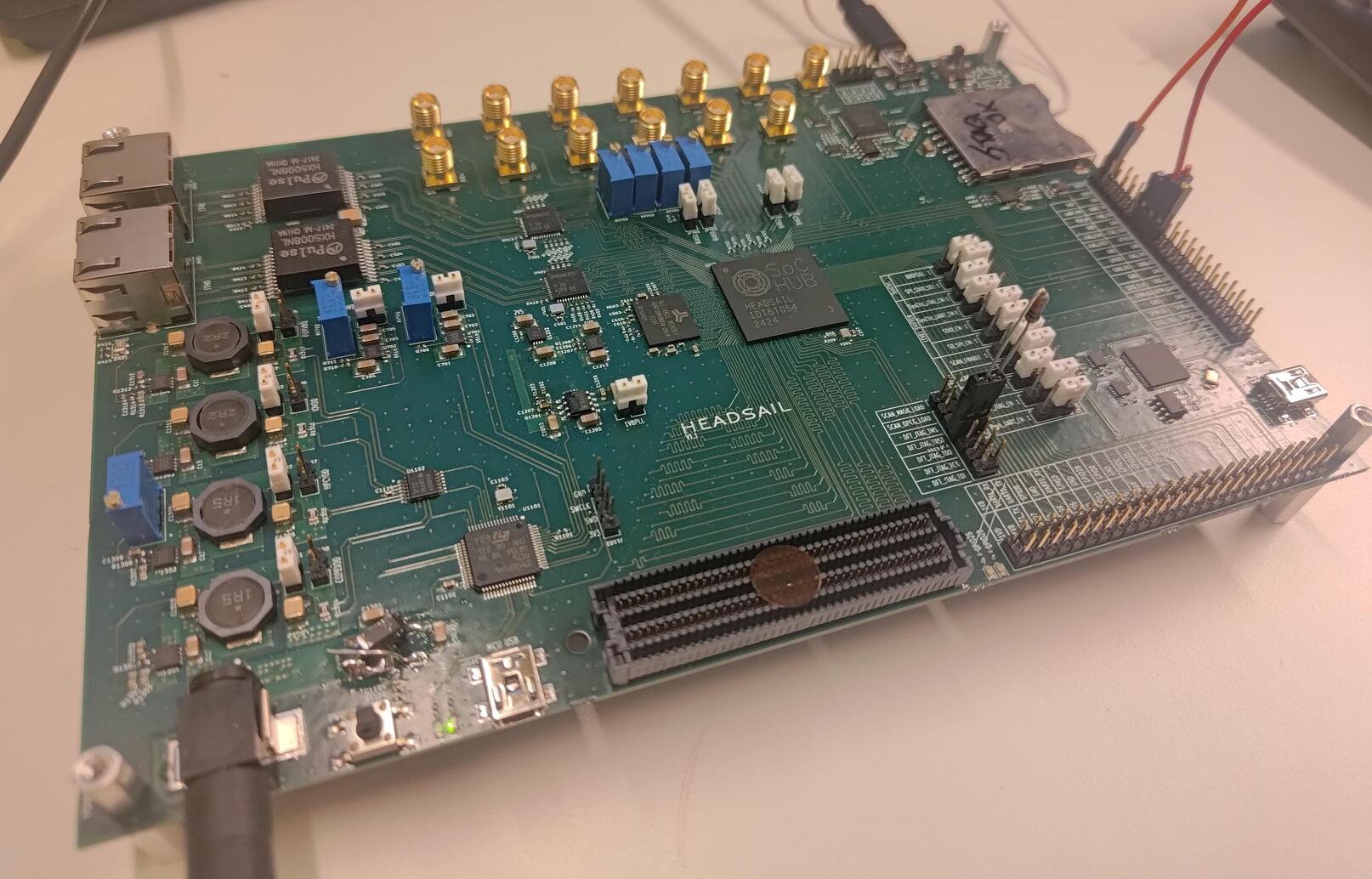

Although CPC knows of multiple tapeouts of TCE/OpenASIP designed cores in the past, thanks to the excellent SoC Hub initiative, this is the first successful public tapeout done in the University setting by the group. Beaivi was integrated into SoC Hub’s 3rd heterogenous multiprocessor SoC test chip called Headsail.

The architecture of Beaivi is a customized DSP design targeted to run in various very low power and ultra-low form factor scenarios. The envisioned applications include 1D signal processing with 1D CNNs such as detecting motor failure from a vibration signal, audio-based wake-up of larger processors and low latency image coding for edge offloading from small wireless devices such as nano/pico drones.

For the CPC group's research, this test chip provides a silicon proof of multiple architecture feature ideas, including programmable dictionary compression and the RISC-V-TTA multi-ISA mode, among other still-to-publish novel features. After the successful initial wake-up and testing of the processor done last week, the group continues to develop a real-world demonstrator using the DSP and run microbenchmarks to write a detailed publication of the processor’s interesting aspects.

Stay tuned for more!