The second System-on-Chip developed by SoC Hub has been taped out

The first chip Ballast was taped out late 2021. The chips arrived in June 2022, and after that, a successful chip wake-up testing was carried out. Most of the key functionalities were brought up in record breaking time of one day from receiving the chips to the CPU boot.

The major prerequisites for the project, such as the infrastructure and the agreements, were set up before the first tape-out and this enabled the development of Tackle to proceed quickly right after the first phase of the project.

The success of Ballast together with exceeding features enabled the project partners to focus on the development of the new IPs. Keeping up with ambitious plan of taping out yearly also requires project execution to be interleaved. To avoid challenges of project dependencies, the focus with the Tackle chip was on developing completely new SoC platform and connectivity IPs. The programmable DMA controller, LP-DDR2 memory controller, and High Speed Serdes datalink were designed, verified and finally taped out as part of the chip.

In the development of Tackle, agile project practices were constantly applied to reach the project targets with given schedule and other resources. In RTL design and hardware-dependent software development, the level of automation was increased by applying and improving the free open-source Kactus2 IP-XACT tool, developed by Tampere University researchers.

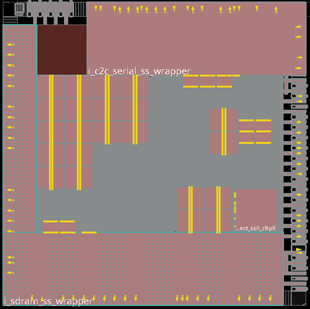

The Tackle die area is 4 mm2 and it is being fabricated on TSMC 22nm Ultra-Low Leakage technology and assembled to 88 pin QFN IC package. The developed new IPs are essential in reaching the project’s targets for the third chip Headsail focusing on high-performance computing on low-power technologies. The designing of the third chip has already started and it will be taped out next autumn.

Headed by Tampere University and Nokia, the project consortium comprises CoreHW, VLSI Solution, TTTEch Flexibilis, Procemex, Wapice and Cargotec as partners. The SoC Hub team is interested in rapid design flow time, and the leading idea of the project is to keep the pace of developing one chip per year.